- You are here:

- Verification Platform

VERIFICATION PLATFORM

Software Product Solutions

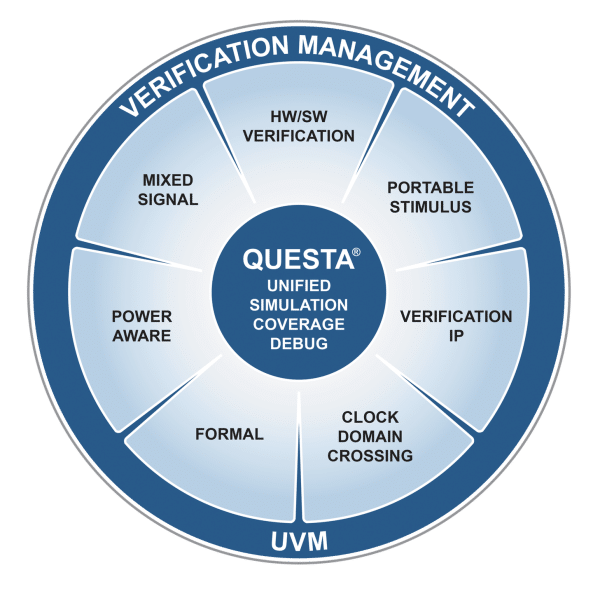

Questa® – Verification Solutions

Questa® Advanced Simulator

The Questa® Advanced Simulator is one of the most powerful verification solutions for complex FPGA and system-on-chip designs as well as IC designs with full native support for VHDL, Verilog, SystemVerilog, SystemC, SVA, UPF and UVM. It is the core simulation and debug engine of the Questa Verification Solution.

The complex designs are verified at various levels of abstraction from TLM (Transaction Level Modeling) to RTL, gate, and transistor-level abstraction.

Multiple powerful verification methodologies, including Assertion-Based Verification (ABV), Open Verification- (OVM), and Universal Verification Methodology (UVM), increase productivity through automation and reusability of testbenches.

- High performance

- Assertion-based Verification

- Test automation through Constrained-random stimulus

- Verification Management

- Integrated multi-language Debugging

- Power Aware Verification

- Multi-core simulation

- UMV made easy through UVM Framework

More information

Fields marked with * are mandatory.

Fields marked with * are mandatory.

UVM Framework I UVM made easy for FPGA Designers

UVM Framework is a combination of a class library and a code generator, delivered as part of the Questa® Verification Solution that enables you to build a UVM testbench within an hour. Providing an UVM architecture and reuse methodology, it allows verification teams, whether they are experienced or new to UVM, to assemble operational UVM testbenches in a very short time.

Fields marked with * are mandatory.

Questa® Verification IP

Comprehensive Verification IPs

The Questa® Verification IP (QVIP) solutions consist of a performance-optimized library of standard SystemVerilog UVM components for simulating ARM® AMBA®, Ethernet, MIPI®, PCIe®, USB, memory models, and many other protocols. By using QVIP engineers can focus on the design.

More information

Fields marked with * are mandatory.

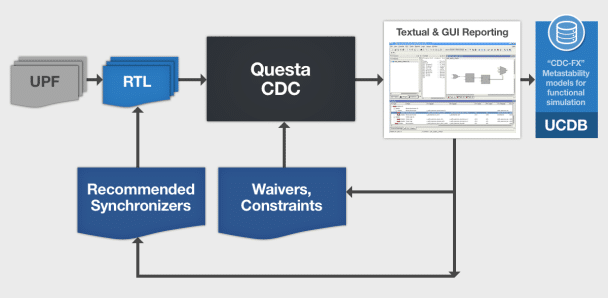

Questa® Clock-Domain Crossing (CDC) Verifikation

Metastabilty from the intermixing of multiple clock signals is not modelled by simulation. Unless you leverage exhaustive, automated Clock Domain Crossing (CDC) analyses to identify and correct problem areas, you will inevitably suffer unpredictable behavior when the chip samples come back from the fab.

Bottom-line

Automated CDC verification solutions are mandatory for multi-clock designs.

More information

Fields marked with * are mandatory.

Questa® Formal Verification Apps

Questa® formal-based technologies offer a broad spectrum of formal solutions and applications which complement simulation in a number of key areas. Questa® Formal Verification Apps boost verification efficiency and design quality by exhaustively addressing verification tasks which are difficult to complete with traditional methods, yet do not require formal or assertion-based verification experience. Siemens EDA, formerly Mentor Graphics, has created a wide ranging portfolio of formal verification apps targeting today’s verification challenges, but are automated to enable non-experts to leverage this technology with minimal coaching:

Questa® AutoCheck App I for FPGA Design and IC Design

Automatic detection of common RTL coding errors

Questa® AutoCheck is a fully-automatic formal bug hunting app that finds bugs due to common RTL coding errors. AutoCheck makes it possible to eliminate a wide range of bugs with low effort. Neither a testbench nor assertions are required to be available, making it possible to start formally verifying designs as soon as the RTL code is written.

Questa® X-Check App I for IC Design

Automated, exhaustive X-state verification

The automated Questa® X-Check app analyses your RTL design, then uses formal engines under-the-hood to exhaustively identify ‘X’ propagation issues in your RTL. No knowledge of formal or property specification languages is required.

Questa® CoverCheck App I for FPGA Design and IC Design

Automating code coverage closure

Questa® CoverCheck is an automatic formal solution for achieving code coverage closure faster. The tool addresses an incontrovertible fact of verification: no matter the combination of techniques used, and even after running an exhaustive battery of tests, some fraction of uncovered code always remains.

Questa® PropGen App I for FPGA Design and IC Design

Automating assertion-based verification for simulation, formal, and hardware-assisted verification

Questa® Property Generation (PropGen) automates assertion-based verification by automatically generating human and machine readable SVA properties from your RTL and testbench.

Questa® Connectivity Check App I for IC Design

Exhaustive, rapid verification of static and dynamic IP & SoC connectivity

The Questa® Connectivity Check app is a fully automated solution for exhaustively verifying static and dynamic connectivity against your clear text CSV or IP-XACT specification.

Questa® Sequential Logic Equivalence Check App I for IC Design

Automated, exhaustive Sequential Logic Equivalence Check (SLEC)

Using the “specification” RTL and the “implementation” RTL as input, the Questa® SLEC formal app automatically compares the two code blocks using an exhaustive formal analysis.

More Information

Questa® Register Check App I for IC Design

Automated, exhaustive memory-mapped register verification

The Questa® Register Check app is a fully automated solution for exhaustively verifying control & status register behavior against your CSV or IP-XACT register specification.

Questa® Secure Check App I for IC Design

Exhaustive verification of secure paths to critical hardware storage

The Questa® Secure Check app is a fully automated solution for exhaustively verifying that only the paths you specify can reach security or safety-critical storage elements.

Questa® Formal Assertion Library App I for FPGA Design and IC Design

Assertion-based verification IP optimized for high performance formal analysis

The Questa Formal Assertion Library provides SystemVerilog Assertion (SVA) packages and examples to verify designs with industry standard protocols; using the Questa Property Checking (PropCheck) application.

Questa® Property Checking App I for FPGA Design and IC Design

Exhaustive verification long before simulation test environments are available

With only a few properties to define the intended behavior and input signal constraints, Questa® Property Checking (PropCheck) can exhaustively verify your RTL – without a testbench! A familiar waveform interface shows failures or successful signal patterns, and the coverage progress is reported in Accellera-standard Unified Coverage DataBase (UCDB) format.

Questa® Post Silicon Debug App I for IC Design

Using Formal Analysis to rapidly root cause post silicon bugs and validate fixes

The Questa® Post Silicon Debug app leverages formal analysis, as well as property synthesis, to rapidly give you the observability you need to root cause bugs in logic deep within the SoC, and prove fixes don’t break anything else.

More information

Fields marked with * are mandatory.

Sources of information on verification

Verification Academy from Siemens EDA

Verification Academy is the most comprehensive, online resource for specific knowledge on FPGA and IC verification.

Verification Horizon

Verification Horizon, a publication by Siemens EDA-A Siemens Business, provides expert and hands-on knowledge of state-of-the-art verification methods.

Verification Horizon Blog

Updates on concepts, standards, methods, and examples to help you understand what advanced functional verification technologies can do and how to use them most effectively. Listen to verification experts Dennis Brophy, Harry Foster, Tom Fitzpatrick and others.

Speaker: Neil Rattray, OneSpin: A Siemens Business

Speaker: Neil Rattray, OneSpin: A Siemens Business  Speaker: Espen Tallaksen, EmLogic AS

Speaker: Espen Tallaksen, EmLogic AS  Speaker: Hans-Jürgen Schwender, TRIAS mikrolektronik

Speaker: Hans-Jürgen Schwender, TRIAS mikrolektronik Speaker: Faïçal Chtourou, Siemens EDA

Speaker: Faïçal Chtourou, Siemens EDA

Speaker: Joachim Müller, Efinix Inc

Speaker: Joachim Müller, Efinix Inc  Speaker: Dr. Markus Jäger, SciCaTec

Speaker: Dr. Markus Jäger, SciCaTec Speaker: David Lidrbauch, Siemens EDA (früher Mentor Graphics)

Speaker: David Lidrbauch, Siemens EDA (früher Mentor Graphics) Speaker: Eugen Krassin, LEC2

Speaker: Eugen Krassin, LEC2 Speaker: Harry Foster

Speaker: Harry Foster Speaker: Stefan Bauer

Speaker: Stefan Bauer Speaker: Tobias Baumann

Speaker: Tobias Baumann Speaker: Hans-Jürgen Schwender

Speaker: Hans-Jürgen Schwender Speaker: Frédéric Leens

Speaker: Frédéric Leens Speaker: Stefan Bauer

Speaker: Stefan Bauer Speaker: Nigel Woolaway

Speaker: Nigel Woolaway